In elettronica, con Dual In-line Package (DIP) si indica un particolare formato di contenitore di un dispositivo elettronico utilizzato per i circuiti integrati (come microcontrollori o microprocessori) o per file di componenti discreti uguali (come interruttori a levetta). Il DIP è di forma rettangolare, con due file parallele di piedini (o pin) disposti sui lati maggiori e piegati in modo da essere quasi perpendicolari alla superficie del rettangolo. Generalmente l'indicazione DIP è seguita da un numero che indica la quantità totale di piedini del dispositivo: ad esempio, DIP20 ha 20 piedini, 10 per ogni lato maggiore.

Storia

[modifica | modifica wikitesto]Il formato DIP fu inventato da Don Forbes, Rex Rice e Bryant "Buck" Rogers nel 1964 presso Fairchild,[1] che lo iniziò ad usare nel 1965 allo scopo di ottimizzare la disposizione e la compattezza dei chip presenti su una stessa scheda elettronica (precedentemente si usavano formati circolari).[2] La possibilità di realizzare singole schede relativamente piccole contenenti tutti i dispositivi integrati necessari ha permesso lo sviluppo di sistemi complessi come i computer.

Pur essendo comunque grandi, se paragonati alle effettive dimensioni dei circuiti integrati al loro interno, i DIP sono stati la spina dorsale dell'industria microelettronica degli anni settanta – ottanta. Alla fine del XX secolo, con l'avvento della tecnologia di montaggio superficiale SMT (Surface-Mount Technology), è stato possibile ridurre sensibilmente le dimensioni dei dispositivi elettronici adoperando nuovi formati come il PLCC (Plastic Leaded Chip Carrier) o il SOIC (Small Outline Integrated Circuit). Oggigiorno i formati DIP sono ancora utilizzati per lo sviluppo di prototipi mediante basette sperimentali (breadboard).

Varianti

[modifica | modifica wikitesto]Esistono diverse varianti del formato DIP, caratterizzate da diversi materiali di cui sono costituite:

- Ceramic Dual In-line Package (CERDIP)

- Plastic Dual In-line Package (PDIP)

- Shrink Plastic Dual In-line Package (SPDIP) – Una versione più piccola del PDIP, con un pitch di 1,778 mm (vedi DIMENSIONI).

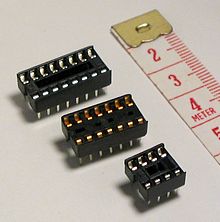

Talvolta, un dispositivo in formato DIP viene inserito ad incastro in appositi zoccoli saldati sulla scheda elettronica che lo ospita. Questo sistema permette di sostituire il chip in caso di malfunzionamento e di evitare il suo danneggiamento a causa dell'elevato calore generato dall'operazione di saldatura.

Dimensioni

[modifica | modifica wikitesto]

I DIP più comuni hanno una spaziatura tra i pin (pitch) di 2,54 mm (0,1 pollici o 100 mil) ed una larghezza di 7,62 mm (0,3 pollici o 300 mil) o 15,24 mm (0,6 pollici o 600 mil). Tipicamente il numero (sempre pari) di pin varia tra gli 8 ed i 24 per i DIP di larghezza 7,62 mm e tra i 24 ed i 40 per i formati da 15,24 mm. Esistono varianti meno comuni, come i DIP da 4 e 28 pin per i formati larghi 7,62 mm e quelli da 36, 48 o 52 pin per i formati larghi 15,24 mm.

Nei Paesi dell'ex Blocco orientale era in uso un formato DIP con pitch di 2,5 mm. Alcuni chip, come il Motorola 68000 e lo Zilog Z180, utilizzavano un numero di pin pari a 64, il massimo utilizzato per un formato DIP.[3]

Numerazione dei pin

[modifica | modifica wikitesto]

I DIP hanno una tacca incisa (o un punto disegnato) su un'estremità della loro superficie superiore come riferimento per il conteggio dei pin. Per poter individuare correttamente i pin del dispositivo bisogna mantenere il chip in modo da guardare la superficie superiore, facendo sì che l'asse di quest'ultima sia parallelo al suolo; assicurandosi che la tacca (o il punto disegnato) sia disposta verso l'alto, lo standard prevede che il pin numero 1 sia quello più in alto della fila sinistra.

I pin dal 2 in poi sono numerati in senso antiorario. L'ultimo pin è chiaramente quello più in alto nella fila destra.

Note

[modifica | modifica wikitesto]- ^ Dummer, G.W.A. Electronic Inventions and Discoveries 2nd ed. Pergamon Press ISBN 0-08-022730-9

- ^ Fairchild fu la prima ad utilizzare un formato DIP per i suoi processori, su computerhistory.org, Computer Museum History. URL consultato il 20 novembre 2010.

- ^ Sung-Mo Kang, Leblebici, Yusuf, CMOS digital integrated circuits (3rd Edition), McGraw-Hill, 2002, p. 42, ISBN 0-07-246053-9.

Bibliografia

[modifica | modifica wikitesto]- Intel (1996). Packaging (databook). ISBN 1-55512-254-X.

Voci correlate

[modifica | modifica wikitesto]Altri progetti

[modifica | modifica wikitesto] Wikimedia Commons contiene immagini o altri file sul dual in-line package

Wikimedia Commons contiene immagini o altri file sul dual in-line package

Collegamenti esterni

[modifica | modifica wikitesto]- DIP, su Treccani.it – Enciclopedie on line, Istituto dell'Enciclopedia Italiana.

- (EN) Denis Howe, Dual in-line package, in Free On-line Dictionary of Computing. Disponibile con licenza GFDL

- Differenze tra i packages DIP, PDIP, SPDIP e SDIP, su settorezero.com.